# IDT™ Interprise™ Integrated Communications Processor

79RC32351

RISController

### Features List

#### RC32300 32-bit Microprocessor

- Enhanced MIPS-II ISA

- Enhanced MIPS-IV cache prefetch instruction

- DSP Instructions

- MMU with 16-entry TLB

- 8kB Instruction cache, 2-way set associative

- 2kB Data cache, 2-way set associative

- Per line cache locking

- Write-through and write-back cache management

- Debug interface through the EJTAG port

- Big or little endian support

#### Interrupt Controller

Allows status of each interrupt to be read and masked

#### UARTs

- Two 16550 Compatible UARTs

- Baud rate support up to 1.5 Mb/s

#### Counter/Timers

Three general purpose 32-bit counter/timers

### General Purpose I/O Pins (GPIOP)

- 32 individually programmable pins:

each pin programmable as input, output, or alternate function,

input can be an interrupt or NMI source,

input can also be active high or active low

- 4 additional, auxiliary GPIO pins can be configured as input or output

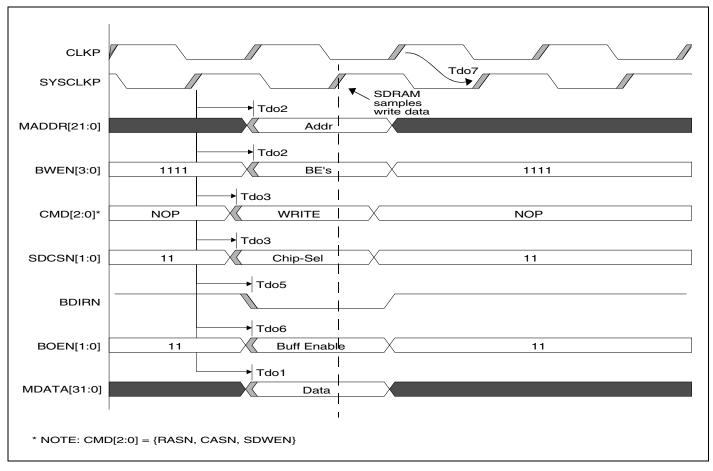

#### SDRAM Controller

- 2 memory banks, non-interleaved, 512 MB total

- 32-bit wide data path

- Supports 4-bit, 8-bit, and 16-bit wide SDRAM chips

- SODIMM support

- Stavs on page between transfers

- Automatic refresh generation

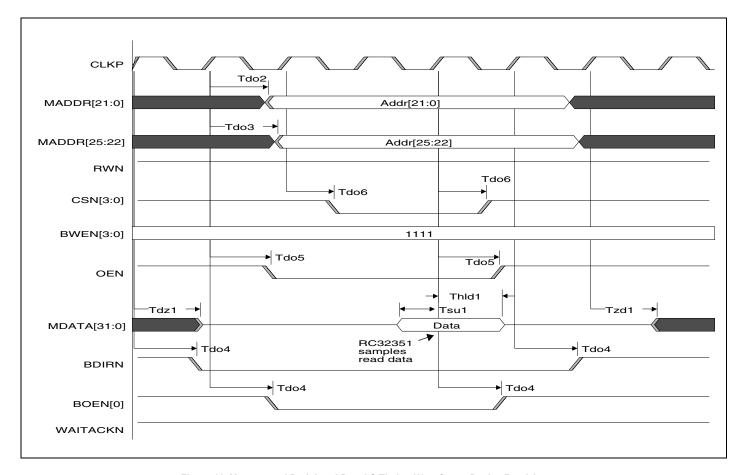

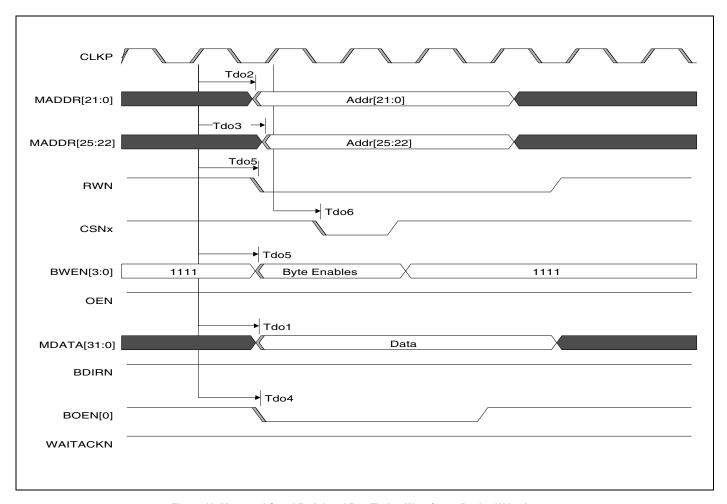

### Peripheral Device Controller

- 26-bit address bus

- 32-bit data bus with variable width support of 8-,16-, or 32-bits

- 8-bit boot ROM support

- 6 banks available, up to 64MB per bank

- Supports Flash ROM, PROM, SRAM, dual-port memory, and peripheral devices

- Supports external wait-state generation, Intel or Motorola style

- Write protect capability

- Direct control of optional external data transceivers

#### System Integrity

- Programmable system watchdog timer resets system on timeout

- Programmable bus transaction times memory and peripheral transactions and generates a warm reset on time-out

#### DMA

- 14 DMA channels

- Services on-chip and external peripherals

- Supports memory-to-memory, memory-to-I/O, and I/O-to-I/O transfers

- Supports flexible descriptor based operation and chaining via linked lists of records (scatter / gather capability)

- Supports unaligned transfers

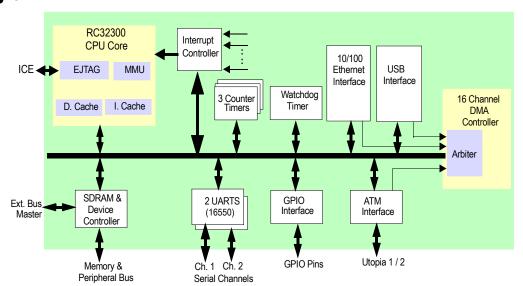

## **Block Diagram**

© 2002 Integrated Device Technology, Inc.

IDT and the IDT logo are trademarks of Integrated Device Technology, Inc.

Supports burst transfers

#### USB

- Revision 1.1 compliant

- USB slave device controller

- Supports a 6<sup>th</sup> USB endpoint

- Full speed operation at 12 Mb/s

- Supports control, interrupt, bulk and isochronous endpoints

- Supports USB remote wakeup

- Integrated USB transceiver

#### EJTAG

- Run-time Mode provides a standard JTAG interface

- Real-Time Mode provides additional pins for real-time trace information

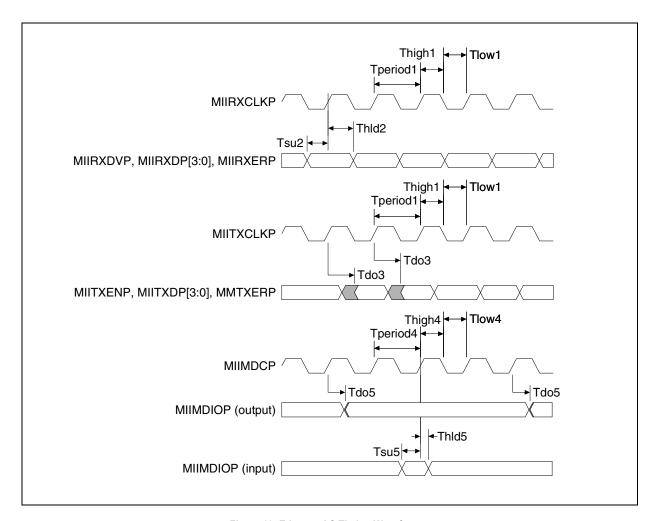

#### Ethernet

- Full duplex support for 10 and 100 Mb/s Ethernet

- IEEE 802.3u compatible Media Independent Interface (MII) with serial management interface

- IEEE 802.3u auto-negotiation for automatic speed selection

- Flexible address filtering modes

- 64-entry hash table based multicast address filtering

#### ATM SAR

- Can be configured as one UTOPIA level 1 interface or 1 UTOPIA level 2 interface with 2 address lines (3 PHYs max)

- Supports 25Mb/s and faster ATM

- Supports UTOPIA data path interface operation at speeds up to 33 MHz

- Supports standard 53-byte ATM cells

- Performs HEC generation and checking

- Cell processing discards short cells and clips long cells

- 16 cells worth of buffering

- UTOPIA modes: 8 cell input buffer and 8 cell output buffer

- Hardware support for CRC-32 generation and checking for AAL5

- Hardware support for CRC-10 generation and checking

- Virtual caching receive mechanism supports reception of any length packet without CPU intervention on up to eight simultaneously active receive channels

- Frame Mode transmit mechanism supports transmission of any length packet without CPU intervention

#### System Features

- JTAG interface (IEEE Std. 1149.1 compatible)

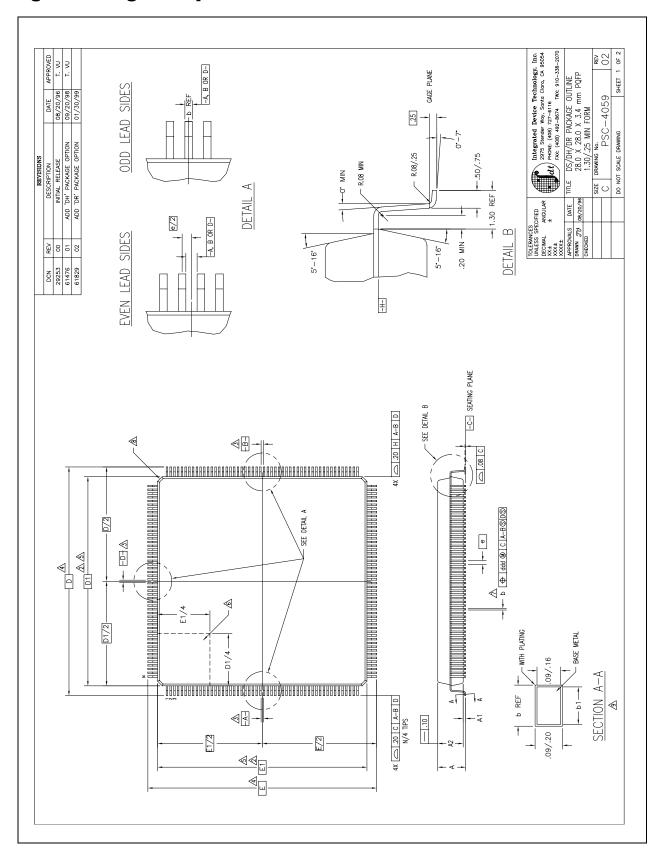

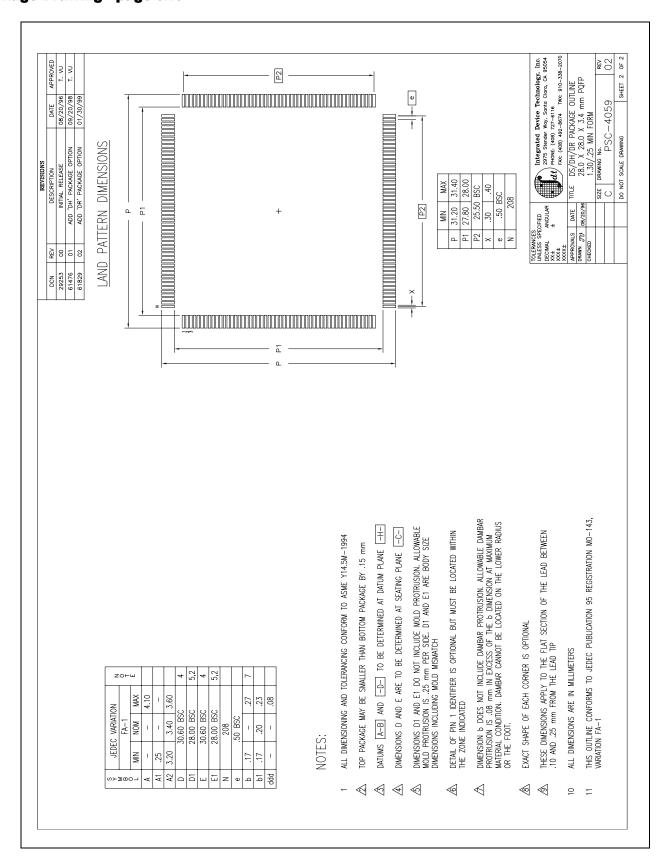

- 208 pin PQFP package

- 2.5V core supply and 3.3V I/O supply

- Up to 133 MHz pipeline frequency and up to 66 MHz bus frequency

Figure 2 Example of xDSL Residential Gateway Using RC32351

### **Device Overview**

The RC32351 is a "System on a Chip" which contains a high performance 32-bit microprocessor. The microprocessor core is used extensively at the heart of the device to implement the most needed functionalities in software with minimal hardware support. The high performance microprocessor handles diverse general computing tasks and specific application tasks that would have required dedicated hardware. Specific application tasks implemented in software can include routing functions, fire wall functions, modem emulation, ATM SAR emulation, and others.

The RC32351 meets the requirements of various embedded communications and digital consumer applications. It is a single chip solution that incorporates most of the generic system functionalities and application specific interfaces that enable rapid time to market, very low cost systems, simplified designs, and reduced board real estate.

#### **CPU Execution Core**

The RC32351 is built around the RC32300 32-bit high performance microprocessor core. The RC32300 implements the enhanced MIPS-II ISA and helps meet the real-time goals and maximize throughput of communications and consumer systems by providing capabilities such as a prefetch instruction, multiple DSP instructions, and cache locking. The DSP instructions enable the RC32300 to implement 33.6 and 56kbps modem functionality in software, removing the need for external dedicated hardware. Cache locking guarantees real-time performance by holding critical DSP code and parameters in the cache for immediate availability. The microprocessor also implements an on-chip MMU with a TLB, making the it fully compliant with the requirements of real time operating systems.

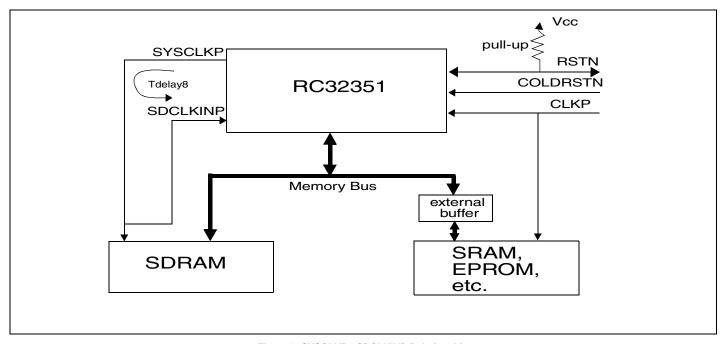

### **Memory and IO Controller**

The RC32351 incorporates a flexible memory and peripheral device controller providing support for SDRAM, Flash ROM, SRAM, dual-port memory, and other I/O devices. It can interface directly to 8-bit boot ROM for a very low cost system implementation. It enables access to high bandwidth external memory (200 MB/sec peak) at very low system costs. It also offers various trade-offs in cost / performance for the main memory architecture. The timers implemented on the RC32351 satisfy the requirements of most RTOS.

#### **DMA Controller**

The DMA controller off-loads the CPU core from moving data among the on-chip interfaces, external peripherals, and memory. The DMA controller supports scatter / gather DMA with no alignment restrictions, appropriate for communications and graphics systems.

#### **Ethernet Interface**

The RC32351 contains an on-chip Ethernet MAC capable of 10 and 100 Mbps line interface with an MII interface. It supports up to 4 MAC addresses. In a SOHO router, the high performance RC32300 CPU core routes the data between the Ethernet and the ATM interface. In other applications, such as high speed modems, the Ethernet interface can be used to connect to the PC.

#### **USB Device Interface**

The RC32351 includes the industry standard USB device interface to enable consumer appliances to directly connect to the PC.

### **ATM SAR**

The RC32351 includes a configurable ATM SAR that supports a UTOPIA level 1 or a UTOPIA level 2 interface. The ATM SAR is implemented as a hybrid between software and hardware. A hardware block provides the necessary low level blocks (like CRC generation and checking and cell buffering) while the software is used for higher level SARing functions. In xDSL modem applications, the UTOPIA port interfaces directly to an xDSL chip set. In SOHO routers or in a line card for a Layer 3 switch, it provides access to an ATM network.

#### **Enhanced JTAG Interface for ICE**

For low-cost In-Circuit Emulation (ICE), the RC32300 CPU core includes an Enhanced JTAG (EJTAG) interface. This interface consists of two operation modes: Run-Time Mode and Real-Time Mode.

The Run-Time Mode provides a standard JTAG interface for on-chip debugging, and the Real-Time Mode provides additional status pins—PCST[2:0]—which are used in conjunction with the JTAG pins for real-time trace information at the processor internal clock or any division of the pipeline clock.

### **Thermal Considerations**

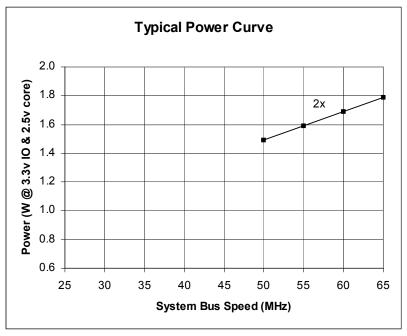

The RC32351 consumes less than 1.5 W peak power and is guaranteed in an ambient temperature range of  $0^{\circ}$  to  $+70^{\circ}$  C (commercial).

### **Revision History**

January 7, 2002: Initial publication.

May 20, 2002: Added values (in place of TBD) to Table 18, Power Consumption.

**September 19, 2002**: Added COLDRSTN Trise1 parameter to Table 5, Reset and System AC Timing Characteristics.

**December 6, 2002**: In Features section, changed UART speed from 115 Kb/s to 1.5 Mb/s.

**December 17, 2002**: Added  $V_{OH}$  parameter to Table 16, DC Electrical Characteristics.

May 25, 2004: In Table 7, signals MIIRXCLK and MIITXCLK, the Min and Max values for 10 Mbps Thigh1/Tlow1 were changed to 140 and 260 respectively and the Min and Max values for 100 Mbps Thigh1/Tlow1 were changed to 14.0 and 26.0 respectively.

### **Pin Description Table**

The following table lists the functions of the pins provided on the RC32351. Some of the functions listed may be multiplexed onto the same pin.

To define the active polarity of a signal, a suffix will be used. Signals ending with an "N" should be interpreted as being active, or asserted, when at a logic zero (low) level. All other signals (including clocks, buses and select lines) will be interpreted as being active, or asserted when at a logic one (high) level.

**Note:** The input pads of the RC32351 do not contain internal pull-ups or pull-downs. Unused inputs should be tied off to appropriate levels. This is especially critical for unused control signal inputs (such as BRN) which, if left floating, could adversely affect the RC32351's operation. Also, any input pin left floating can cause a slight increase in power consumption.

| Name             | Туре       | I/O Type                                  | Description                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

|------------------|------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| System           | <u> </u>   |                                           |                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| CLKP             | I          | Input                                     | <b>System Clock input.</b> This is the system master clock input. The RISCore 32300 pipeline frequency is a multiple (x2, x3, or x4) of this clock frequency. All other logic runs at this frequency or less.                                                                                                                                                        |  |  |  |  |  |  |

| COLDRSTN         | I          | STI <sup>1</sup>                          | <b>Cold Reset.</b> The assertion of this signal low initiates a cold reset. This causes the RC32351 state to be initialized, boot configuration to be loaded, and the internal processor PLL to lock onto the system clock (CLKP).                                                                                                                                   |  |  |  |  |  |  |

| RSTN             | I/O        |                                           | <b>Reset.</b> This bidirectional signal is either driven low or tri-stated, an external pull-up is required to supply the high state. The RC32351 drives RSTN low during a reset (to inform the external system that a reset is taking place) and then tri-states it. The external system can drive RSTN low to initiate a warm reset, and then should tri-state it. |  |  |  |  |  |  |

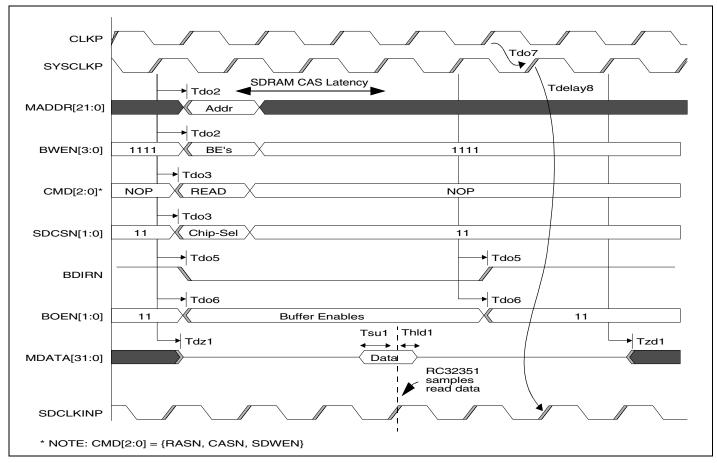

| SYSCLKP          | 0          | High Drive                                | System clock output. This is a buffered and delayed version of the system clock input (CLKP). All SDRAM transaction are synchronous to this clock. This pin should be externally connected to the SDRAMs and to the RC32351 SDCLKINF (SDRAM clock input).                                                                                                            |  |  |  |  |  |  |

| Memory and Perip | pheral Bus |                                           |                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| MADDR[25:0]      | 0          | [21:0] High<br>Drive                      | <b>Memory Address Bus.</b> 26-bit address bus for memory and peripheral accesses. MADDR[20:17] are used for the SODIMM data mask enables if SODIMM mode is selected.                                                                                                                                                                                                 |  |  |  |  |  |  |

|                  |            | Drive with<br>STI                         | MADDR[22] Primary function: General Purpose I/O, GPIOP[27]. MADDR[23] Primary function: General Purpose I/O, GPIOP[28]. MADDR[24] Primary function: General Purpose I/O, GPIOP[29]. MADDR[25] Primary function: General Purpose I/O, GPIOP[30].                                                                                                                      |  |  |  |  |  |  |

| MDATA[31:0]      | I/O        | High Drive                                | Memory Data Bus. 32-bit data bus for memory and peripheral accesses.                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| BDIRN            | 0          | High Drive                                | <b>External Buffer Direction.</b> External transceiver direction control for the memory and peripheral data bus, MDATA[31:0]. It is asserted low during any read transaction, and remains high during write transactions.                                                                                                                                            |  |  |  |  |  |  |

| BOEN[1:0]        | 0          | High Drive                                | <b>External Buffer Output Enable.</b> These signals provide two output enable controls for external data bus transceivers on the memory and peripheral data bus, MDATA. BOEN[0] is asserted low during external device read transactions. BOEN[1] is asserted low during SDRAM read transactions.                                                                    |  |  |  |  |  |  |

| BRN              | I          | STI                                       | <b>External Bus Request.</b> This signal is asserted low by an external master device to request ownership of the memory and peripheral bus.                                                                                                                                                                                                                         |  |  |  |  |  |  |

| BGN              | 0          | Low Drive                                 | <b>External Bus Grant.</b> This signal is asserted low by RC32351 to indicate that RC32351 has relinquished ownership of the local memory and peripheral bus to an external master.                                                                                                                                                                                  |  |  |  |  |  |  |

| WAITACKN         | I          | STI                                       | Wait or Transfer Acknowledge. When configured as wait, this signal is asserted low during a memory and peripheral device bus transaction to extend the bus cycle. When configured as transfer acknowledge, this signal is asserted low during a memory and peripheral device bus transaction to signal the completion of the transaction.                            |  |  |  |  |  |  |

| CSN[5:0]         | 0          | [3:0]<br>High Drive<br>[5:4]<br>Low Drive | <b>Device Chip Select.</b> These signals are used to select an external device on the memory and peripheral bus during device transactions. Each bit is asserted low during an access to the selected external device. CSN[4] Primary function: General purpose I/O, GPIOP[16]. CSN[5] Primary function: General purpose I/O, GPIOP[17].                             |  |  |  |  |  |  |

Table 1 Pin Descriptions (Part 1 of 7)

| Name              | Туре      | I/O Type              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------|-----------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RWN               | 0         | High Drive            | Read or Write. This signal indicates if the transaction on the memory and peripheral bus is a read transaction or a write transaction. A high level indicates a read from an external device, a low level indicates a write to an external device.                                                                                                                                                                                                                  |

| OEN               | 0         | High Drive            | Output Enable. This signal is asserted low when data should be driven by an external device during device read transactions on the memory and peripheral bus.                                                                                                                                                                                                                                                                                                       |

| BWEN[3:0]         | 0         | High Drive            | SDRAM Byte Enable Mask or Memory and I/O Byte Write Enables. These signals are used as data input/output masks during SDRAM transactions and as byte write enable signals during device controller transactions on the memory and peripheral bus. They are active low.  BWEN[0] corresponds to byte lane MDATA[7:0].  BWEN[1] corresponds to byte lane MDATA[15:8].  BWEN[2] corresponds to byte lane MDATA[23:16].  BWEN[3] corresponds to byte lane MDATA[31:24]. |

| SDCSN[1:0]        | 0         | High Drive            | <b>SDRAM Chip Select.</b> These signals are used to select the SDRAM device on the memory and peripheral bus. Each bit is asserted low during an access to the selected SDRAM.                                                                                                                                                                                                                                                                                      |

| RASN              | 0         | High Drive            | SDRAM Row Address Strobe. The row address strobe asserted low during memory and peripheral bus SDRAM transactions.                                                                                                                                                                                                                                                                                                                                                  |

| CASN              | 0         | High Drive            | SDRAM Column Address Strobe. The column address strobe asserted low during memory and peripheral bus SDRAM transactions.                                                                                                                                                                                                                                                                                                                                            |

| SDWEN             | 0         | High Drive            | SDRAM Write Enable. Asserted low during memory and peripheral bus SDRAM write transactions.                                                                                                                                                                                                                                                                                                                                                                         |

| CKENP             | 0         | Low Drive             | SDRAM Clock Enable. Asserted high during active SDRAM clock cycles. Primary function: General Purpose I/O, GPIOP[21].                                                                                                                                                                                                                                                                                                                                               |

| SDCLKINP          | I         | STI                   | <b>SDRAM Clock Input.</b> This clock input is a delayed version of SYSCLKP. SDRAM read data is sampled into the RC32351 on the rising edge of this clock.                                                                                                                                                                                                                                                                                                           |

| ATM Interface     | •         | •                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| ATMINP[11:0]      | I         | STI                   | ATM PHY Inputs. These pins are the inputs for the ATM interface.                                                                                                                                                                                                                                                                                                                                                                                                    |

| ATMIOP[1:0]       | I/O       | Low Drive with STI    | ATM PHY Bidirectional Signals. These pins are the bidirectional pins for the ATM interface.                                                                                                                                                                                                                                                                                                                                                                         |

| ATMOUTP[9:0]      | 0         | Low Drive             | ATM PHY Outputs. These pins are the outputs for the ATM interface.                                                                                                                                                                                                                                                                                                                                                                                                  |

| TXADDR[1:0]       | 0         | Low Drive             | ATM Transmit Address [1:0]. 2-bit address bus used for transmission in Utopia-2 mode.  TXADDR[0] Primary function: General purpose I/O, GPIOP[22].  TXADDR[1] Primary function: General purpose I/O, GPIOP[23].                                                                                                                                                                                                                                                     |

| RXADDR[1:0]       | 0         | Low Drive             | ATM Receive Address [1:0]. 2-bit address bus for receiving in Utopia-2 mode.  RXADDR[0] Primary function: General purpose I/O, GPIOP[24].  RXADDR[1] Primary function: General purpose I/O, GPIOP[25].                                                                                                                                                                                                                                                              |

| General Purpose I | nput/Outp | out                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| GPIOP[0]          | I/O       | Low Drive with STI    | General Purpose I/O. This pin can be configured as a general purpose I/O pin.  Alternate function: UART channel 0 serial output, U0SOUTP.                                                                                                                                                                                                                                                                                                                           |

| GPIOP[1]          | I/O       | Low Drive with STI    | General Purpose I/O. This pin can be configured as a general purpose I/O pin. Alternate function: UART channel 0 serial input, U0SINP.                                                                                                                                                                                                                                                                                                                              |

| GPIOP[2]          | I/O       | Low Drive<br>with STI | General Purpose I/O. This pin can be configured as a general purpose I/O pin.  1st Alternate function: UART channel 0 ring indicator, U0RIN.  2nd Alternate function: JTAG boundary scan tap controller reset, JTAG_TRST_N.                                                                                                                                                                                                                                         |

| GPIOP[3]          | I/O       | Low Drive with STI    | General Purpose I/O. This pin can be configured as a general purpose I/O pin.  Alternate function: UART channel 0 data carrier detect, U0DCRN.                                                                                                                                                                                                                                                                                                                      |

| GPIOP[4]          | I/O       | Low Drive<br>with STI | General Purpose I/O. This pin can be configured as a general purpose I/O pin.  1st Alternate function: UART channel 0 data terminal ready, U0DTRN.  2nd Alternate function: CPU or DMA transaction indicator, CPUP.                                                                                                                                                                                                                                                 |

Table 1 Pin Descriptions (Part 2 of 7)

| Name      | Туре | I/O Type              | Description                                                                                                                                                                                                     |

|-----------|------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIOP[5]  | I/O  |                       | General Purpose I/O. This pin can be configured as a general purpose I/O pin.  Alternate function: UART channel 0 data set ready, U0DSRN.                                                                       |

| GPIOP[6]  | I/O  |                       | General Purpose I/O. This pin can be configured as a general purpose I/O pin.  Alternate function: UART channel 0 request to send, U0RTSN.                                                                      |

| GPIOP[7]  | I/O  |                       | General Purpose I/O. This pin can be configured as a general purpose I/O pin. Alternate function: UART channel 0 clear to send, U0CTSN.                                                                         |

| GPIOP[8]  | I/O  | Low Drive<br>with STI | General Purpose I/O. This pin can be configured as a general purpose I/O pin.  1st Alternate function: UART channel 1 serial output, U1SOUTP.  2nd Alternate function: Active DMA channel code, DMAP[3].        |

| GPIOP[9]  | I/O  |                       | General Purpose I/O. This pin can be configured as a general purpose I/O pin.  1st Alternate function: UART channel 1 serial input, U1SINP.  2nd Alternate function: Active DMA channel code, DMAP[2].          |

| GPIOP[10] | I/O  | with STI              | General Purpose I/O. This pin can be configured as a general purpose I/O pin.  1st Alternate function: UART channel 1 data terminal ready, U1DTRN.  2nd Alternate function: ICE PC trace status, EJTAG_PCST[0]. |

| GPIOP[11] | I/O  | Low Drive<br>with STI | General Purpose I/O. This pin can be configured as a general purpose I/O pin.  1st Alternate function: UART channel 1 data set ready, U1DSRN.  2nd Alternate function: ICE PC trace status, EJTAG_PCST[1].      |

| GPIOP[12] | I/O  |                       | General Purpose I/O. This pin can be configured as a general purpose I/O pin.  1st Alternate function: UART channel 1 request to send, U1RTSN.  2nd Alternate function: ICE PC trace status, EJTAG_PCST[2].     |

| GPIOP[13] | I/O  | with STI              | General Purpose I/O. This pin can be configured as a general purpose I/O pin.  1st Alternate function: UART channel 1 clear to send, U1CTSN.  2nd Alternate function: ICE PC trace clock, EJTAG_DCLK.           |

| GPIOP[14] | I/O  | Low Drive with STI    | General Purpose I/O. This pin can be configured as a general purpose I/O pin.                                                                                                                                   |

| GPIOP[15] | I/O  | Low Drive with STI    | General Purpose I/O. This pin can be configured as a general purpose I/O pin.                                                                                                                                   |

| GPIOP[16] | I/O  | High Drive            | General Purpose I/O. This pin can be configured as a general purpose I/O pin.  Alternate function: Memory and peripheral bus chip select, CSN[4].                                                               |

| GPIOP[17] | I/O  | High Drive            | General Purpose I/O. This pin can be configured as a general purpose I/O pin.  Alternate function: Memory and peripheral bus chip select, CSN[5].                                                               |

| GPIOP[18] | I/O  | Low Drive<br>with STI | General Purpose I/O. This pin can be configured as a general purpose I/O pin.  Alternate function: External DMA device request, DMAREQN.                                                                        |

| GPIOP[19] | I/O  |                       | General Purpose I/O. This pin can be configured as a general purpose I/O pin. Alternate function: External DMA device done, DMADONEN.                                                                           |

| GPIOP[20] | I/O  | Low Drive<br>with STI | General Purpose I/O. This pin can be configured as a general purpose I/O pin.  Alternate function: USB start of frame, USBSOF.                                                                                  |

| GPIOP[21] | I/O  | Low Drive<br>with STI | General Purpose I/O. This pin can be configured as a general purpose I/O pin.  Alternate function: SDRAM clock enable CKENP.                                                                                    |

| GPIOP[22] | I/O  | Low Drive<br>with STI | General Purpose I/O. This pin can be configured as a general purpose I/O pin.  Alternate function: ATM transmit PHY address, TXADDR[0].                                                                         |

| GPIOP[23] | I/O  | Low Drive<br>with STI | General Purpose I/O. This pin can be configured as a general purpose I/O pin.  1st Alternate function: ATM transmit PHY address, TXADDR[1].  2nd Alternate function: Active DMA channel code, DMAP[0].          |

Table 1 Pin Descriptions (Part 3 of 7)

| Name      | Туре | I/O Type              | Description                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

|-----------|------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| GPIOP[24] | I/O  | Low Drive<br>with STI | General Purpose I/O. This pin can be configured as a general purpose I/O pin.  Alternate function: ATM receive PHY address, RXADDR[0].                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| GPIOP[25] | I/O  | Low Drive<br>with STI | General Purpose I/O. This pin can be configured as a general purpose I/O pin.  1st Alternate function: ATM receive PHY address, RXADDR[1].  2nd Alternate function: Active DMA channel code, DMAP[1].                                                                                                                                     |  |  |  |  |  |  |  |

| GPIOP[26] | I/O  | Low Drive with STI    | General Purpose I/O. This pin can be configured as a general purpose I/O pin.                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| GPIOP[27] | I/O  | Low Drive with STI    | eneral Purpose I/O. This pin can be configured as a general purpose I/O pin. ternate function: Memory and peripheral bus address, MADDR[22].                                                                                                                                                                                              |  |  |  |  |  |  |  |

| GPIOP[28] | I/O  | Low Drive with STI    | General Purpose I/O. This pin can be configured as a general purpose I/O pin.  Alternate function: Memory and peripheral bus address, MADDR[23].                                                                                                                                                                                          |  |  |  |  |  |  |  |

| GPIOP[29] | I/O  | Low Drive with STI    | General Purpose I/O. This pin can be configured as a general purpose I/O pin. Alternate function: Memory and peripheral bus address, MADDR[24].                                                                                                                                                                                           |  |  |  |  |  |  |  |

| GPIOP[30] | I/O  | Low Drive with STI    | General Purpose I/O. This pin can be configured as a general purpose I/O pin. Alternate function: Memory and peripheral bus address, MADDR[25].                                                                                                                                                                                           |  |  |  |  |  |  |  |

| GPIOP[31] | I/O  | Low Drive<br>with STI | General Purpose I/O. This pin can be configured as a general purpose I/O pin.  1ST Alternate function: DMA finished, DMAFIN.  2nd Alternate function: EJTAG/ICE reset, EJTAG_TRST_N.                                                                                                                                                      |  |  |  |  |  |  |  |

| GPIOP[32] | I/O  | High Drive            | General Purpose I/O. This pin can be configured as an auxiliary general purpose I/O pin.                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| GPIOP[33] | I/O  | Low Drive with STI    | General Purpose I/O. This pin can be configured as an auxiliary general purpose I/O pin.                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| GPIOP[34] | I/O  | High Drive            | General Purpose I/O. This pin can be configured as an auxiliary general purpose I/O pin.                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| GPIOP[35] | I/O  | Low Drive with STI    | General Purpose I/O. This pin can be configured as an auxiliary general purpose I/O pin.                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| DMA       | •    |                       |                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| DMAFIN    | 0    | Low                   | <b>External DMA finished.</b> This signal is asserted low by the RC32351 when the number of bytes specified in the DMA descriptor have been transferred to or from an external device. Primary function: General Purpose I/O, GPIOP[31]. At reset, this pin defaults to primary function GPIOP[31]. 2nd Alternate function: EJTAG_TRST_N. |  |  |  |  |  |  |  |

| DMAREQN   | I    | STI                   | External DMA Device Request. The external DMA device asserts this pin low to request DMA service.  Primary function: General purpose I/O, GPIOP[18]. At reset, this pin defaults to primary function GPIOP[18].                                                                                                                           |  |  |  |  |  |  |  |

| DMADONEN  | I    | STI                   | <b>External DMA Device Done</b> . The external DMA device asserts this signal low to inform the RC32351 that it is done with the current DMA transaction.  Primary function: General purpose I/O, GPIOP[19]. At reset, this pin defaults to primary function GPIOP[19].                                                                   |  |  |  |  |  |  |  |

| USB       | •    |                       |                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| USBCLKP   | I    | STI                   | USB Clock. 48 MHz clock input used as time base for the USB interface.                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| USBDN     | I/O  | USB                   | USB D- Data Line. This is the negative differential USB data signal.                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| USBDP     | I/O  | USB                   | USB D+ Data Line. This is the positive differential USB data signal.                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| USBSOF    | 0    | Low Drive             | USB start of frame. Primary function: General Purpose I/O, GPIOP[20]. At reset, this pin defaults to primary function GPIOP[20].                                                                                                                                                                                                          |  |  |  |  |  |  |  |

| Ethernet  | ·    |                       |                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| MIICOLP   | I    | STI                   | MII Collision Detected. This signal is asserted by the ethernet PHY when a collision is detected.                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| MIICRSP   | ı    | STI                   | MII Carrier Sense. This signal is asserted by the ethernet PHY when either the transmit or receive medium is not idle.                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| MIIMDCP   | 0    | Low Drive             | MII Management Data Clock. This signal is used as a timing reference for transmission of data on the management interface.                                                                                                                                                                                                                |  |  |  |  |  |  |  |

Table 1 Pin Descriptions (Part 4 of 7)

| Name          | Туре | I/O Type  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|---------------|------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| MIIMDIOP      | I/O  |           | MII Management Data. This bidirectional signal is used to transfer data between the station management entity and the ethernet PHY.                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| MIIRXCLKP     | I    | STI       | MII Receive Clock. This clock is a continuous clock that provides a timing reference for the reception of data.                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| MIIRXDP[3:0]  | I    | STI       | III Receive Data. This nibble wide data bus contains the data received by the ethernet PHY.                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| MIIRXDVP      | I    | STI       | MII Receive Data Valid. The assertion of this signal indicates that valid receive data is in the MII receive data bus.                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| MIIRXERP      | I    | STI       | MII Receive Error. The assertion of this signal indicates that an error was detected somewhere in the ethernet frame currently being sent in the MII receive data bus.                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| MIITXCLKP     | 1    | STI       | MII Transmit Clock. This clock is a continuous clock that provides a timing reference for the transfer of transmit data.                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| MIITXDP[3:0]  | 0    | Low Drive | MII Transmit Data. This nibble wide data bus contains the data to be transmitted.                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| MIITXENP      | 0    | Low Drive | MII Transmit Enable. The assertion of this signal indicates that data is present on the MII for transmission.                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| MIITXERP      | 0    | Low Drive | MII Transmit Coding Error. When this signal is asserted together with MIITXENP, the ethernet PHY will transmit symbols which are not valid data or delimiters.                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| EJTAG         |      | •         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| JTAG_TCK      | I    | STI       | JTAG Clock. This is an input test clock, used to shift data into or out of the boundary scan logic. This signal requires an external resistor, listed in Table 14.                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| JTAG_TDI      | I    | STI       | JTAG Data Input. This is the serial data shifted into the boundary scan logic. This signal requires an external resistor, listed in Table 14. This is also used to input EJTAG_DINTN during EJTAG/ICE mode. EJTAG_DINTN is an interrupt to switch the PC trace mode off.                                                                                                                                                                                                       |  |  |  |  |

| JTAG_TDO      | 0    | Low Drive | JTAG Data Output. This is the serial data shifted out from the boundary scan logic. When no data is being shifted out, this signal is tri-stated. This signal requires an external resistor, listed in Table 14. This is also used to output the EJTAG_TPC during EJTAG/ICE mode. EJTAG_TPC is the non-sequential program counter output.                                                                                                                                      |  |  |  |  |

| JTAG_TMS      | I    | STI       | JTAG Mode Select. This input signal is decoded by the tap controller to control test operation. This signal requires an external resistor, listed in Table 14.                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| EJTAG_PCST[0] | 0    | Low Drive | PC trace status. This bus gives the PC trace status information during EJTAG/ICE mode. EJTAG/ICE enable is selected during reset using the boot configuration and overrides the selection of the Primary and Alternate functions. This signal requires an external resistor, listed in Table 14.  Primary function: General Purpose I/O, GPIOP[10].  1st Alternate function: UART channel 1 data terminal ready, U1DTRN.                                                       |  |  |  |  |

| EJTAG_PCST[1] | 0    | Low Drive | PC trace status. This bus gives the PC trace status information during EJTAG/ICE mode. EJTAG/ICE enable is selected during reset using the boot configuration and overrides the selection of the Primary and Alternate functions. This signal requires an external resistor, listed in Table 14.  Primary function: General Purpose I/O, GPIOP[11]. At reset, this pin defaults to primary function GPIOP[11].  1st Alternate function: UART channel 1 data set ready, U1DSRN. |  |  |  |  |

| EJTAG_PCST[2] | 0    | Low Drive | PC trace status. This bus gives the PC trace status information during EJTAG/ICE mode. EJTAG/ICE enable is selected during reset using the boot configuration and overrides the selection of the Primary and Alternate functions. This signal requires an external resistor, listed in Table 14.  Primary function: General Purpose I/O, GPIOP[12].  1st Alternate function: UART channel 1 request to send, U1RTSN.                                                           |  |  |  |  |

| EJTAG_DCLK    | 0    | Low Drive | PC trace clock. This is used to capture address and data during EJTAG/ICE mode. EJTAG/ICE enable is selected during reset using the boot configuration and overrides the selection of the Primary and Alternate functions. This signal requires an external resistor, listed in Table 14.  Primary function: General Purpose I/O, GPIOP[13].  1st Alternate function: UART channel 1 clear to send, U1CTSN.                                                                    |  |  |  |  |

Table 1 Pin Descriptions (Part 5 of 7)

| Name         | Туре | I/O Type  | EJTAG Test Reset. EJTAG_TRST_N is an active-low signal for asynchronous reset of only the EJTAG/ICE controller.  EJTAG_TRST_N requires an external pull-up on the board. EJTAG/ICE enable is selected during reset using the boot configuration and overrides the selection of the Primary and Alternate functions. This signal requires an external resistor, listed in Table 14.  Primary: General Purpose I/O, GPIOP[31]  1st Alternate function: DMA finished output, DMAFIN.                                                  |  |  |  |  |  |  |  |

|--------------|------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| EJTAG_TRST_N | I    | STI       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| JTAG_TRST_N  | I    | STI       | JTAG Test Reset. JTAG_TRST_N is an active-low signal for asynchronous reset of only the JTAG boundary scan controller. JTAG_TRST_N requires an external pull-down on the board that will hold the JTAG boundary scan controller in reset when not in use if selected. JTAG reset enable is selected during reset using the boot configuration and overrides the selection of the Primary and Alternate functions.  Primary function: General Purpose I/O, GPIOP[2].  1st Alternate function: UART channel 0 ring indicator, U0RIN. |  |  |  |  |  |  |  |

| Debug        | •    |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| INSTP        | 0    | Low Drive | <b>Instruction or Data Indicator</b> . This signal is driven high during CPU instruction fetches and low during CPU data transactions on the memory and peripheral bus.                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| CPUP         | 0    | Low Drive | CPU or DMA Transaction Indicator. This signal is driven high during CPU transactions and low during DMA transactions on the memory and peripheral bus if CPU/DMA Transaction Indicator Enable is enabled. CPU/DMA Status mode enable is selected during reset using the boot configuration and overrides the selection of the Primary and Alternate functions. Primary function: General Purpose I/O, GPIOP[4].  1st Alternate function: UART channel 0 data terminal ready U0DTRN.                                                |  |  |  |  |  |  |  |

| DMAP[0]      | 0    | Low Drive | Active DMA channel code. DMA debug enable is selected during reset using the boot configuration and overrides the selection of the Primary and Alternate functions.  Primary function: General Purpose I/O, GPIOP[23].  1st Alternate function: TXADDR[1].                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| DMAP[1]      | 0    | Low Drive | Active DMA channel code. DMA debug enable is selected during reset using the boot configuration and overrides the selection of the Primary and Alternate functions.  Primary function: General Purpose I/O, GPIOP[25].  1st Alternate function: RXADDR[1].                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| DMAP[2]      | 0    | Low Drive | Active DMA channel code. DMA debug enable is selected during reset using the boot configuration and overrides the selection of the Primary and Alternate functions.  Primary function: General Purpose I/O, GPIOP[9].  1st Alternate function: U1SINP.                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| DMAP[3]      | 0    | Low Drive | Active DMA channel code. DMA debug enable is selected during reset using the boot configuration and overrides the selection of the Primary and Alternate functions.  Primary function: General Purpose I/O, GPIOP[8].  1st Alternate function: U1SOUTP.                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| UART         | •    |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| U0SOUTP      | I    | STI       | UART channel 0 serial transmit.  Primary function: General Purpose I/O, GPIOP[0]. At reset, this pin defaults to primary function GPIOP[0].                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| U0SINP       | I    | STI       | UART channel 0 serial receive. Primary function: General Purpose I/O, GPIOP[1]. At reset, this pin defaults to primary function GPIOP[1].                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |

| U0RIN        | I    | STI       | UART channel 0 ring indicator.  Primary function: General Purpose I/O, GPIOP[2]. At reset, this pin defaults to primary function GPIOP[2] if JTAG reset enable is not selected during reset using the boot configuration.  2nd Alternate function: JTAG boundary scan reset, JTAG_TRST_N.                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |

| U0DCRN       | I    | STI       | UART channel 0 data carrier detect. Primary function: General Purpose I/O, GPIOP[3]. At reset, this pin defaults to primary function GPIOP[3].                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

Table 1 Pin Descriptions (Part 6 of 7)

| Name    | Туре | I/O Type  | Description                                                                                                                                                                                                                                                                                              |

|---------|------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| U0DTRN  | 0    | Low Drive | UART channel 0 data terminal ready.  Primary function: General Purpose I/O, GPIOP[4]. At reset, this pin defaults to primary function GPIOP[4] if CPU/DMA Status Mode enable is not selected during reset using the boot configuration.  2nd Alternate function: CPU or DMA transaction indicator, CPUP. |

| U0DSRN  | I    | STI       | UART channel 0 data set ready. Primary function: General Purpose I/O, GPIOP[5]. At reset, this pin defaults to primary function GPIOP[5].                                                                                                                                                                |

| UORTSN  | 0    | Low Drive | UART channel 0 request to send. Primary function: General Purpose I/O, GPIOP[6]. At reset, this pin defaults to primary function GPIOP[6].                                                                                                                                                               |

| U0CTSN  | I    | STI       | UART channel 0 clear to send. Primary function: General Purpose I/O, GPIOP[7]. At reset, this pin defaults to primary function GPIOP[7].                                                                                                                                                                 |

| U0SOUTP | 0    | Low Drive | UART channel 1 serial transmit.  Primary function: General Purpose I/O, GPIOP[8]. At reset, this pin defaults to primary function GPIOP[8] if DMA Debug enable is not selected during reset using the boot configuration.  2nd Alternate function: DMA channel, DMAP[3].                                 |

| U1SINP  | I    | STI       | UART channel 1 serial receive.  Primary function: General Purpose I/O, GPIOP[9]. At reset, this pin defaults to primary function GPIOP[9] if DMA Debug enable is not selected during reset using the boot configuration.  2nd Alternate function: DMA channel, DMAP[2].                                  |

| U1DTRN  | 0    | Low Drive | UART channel 1 data terminal ready.  Primary function: General Purpose I/O, GPIOP[10]. At reset, this pin defaults to primary function GPIOP[10] if ICE Interface enable is not selected during reset using the boot configuration.  Alternate function: PC trace status bit 0, EJTAG_PCST[0].           |

| U1DSRN  | I    | STI       | UART channel 1 data set ready.  Primary function: General Purpose I/O, GPIOP[11]. At reset, this pin defaults to primary function GPIOP[11] if ICE Interface enable is not selected during reset using the boot configuration.  2nd Alternate function: PC trace status bit 1, EJTAG_PCST[1].            |

| U1RTSN  | 0    | Low Drive | UART channel 1 request to send.  Primary function: General Purpose I/O, GPIOP[12]. At reset, this pin defaults to primary function GPIOP[12] if ICE Interface enable is not selected during reset using the boot configuration.  2nd Alternate function: PC trace status bit 2, EJTAG_PCST[2].           |

| U1CTSN  | I    | STI       | UART channel 1 clear to send.  Primary function: General Purpose I/O, GPIOP[13]. At reset, this pin defaults to primary function GPIOP[13] if ICE Interface enable is not selected during reset using the boot configuration.  2nd Alternate function: PC trace clock, EJTAG_DCLK.                       |

Table 1 Pin Descriptions (Part 7 of 7)

### **Boot Configuration Vector**

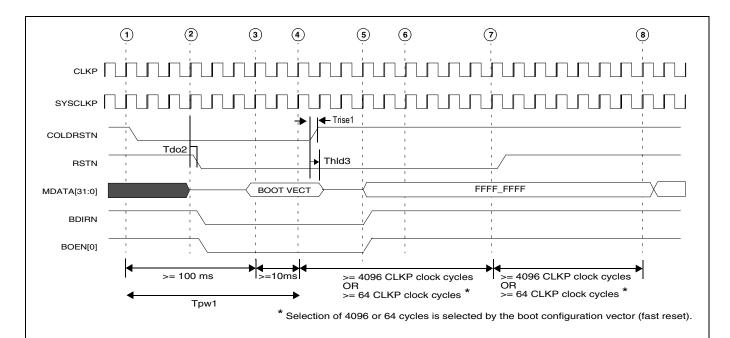

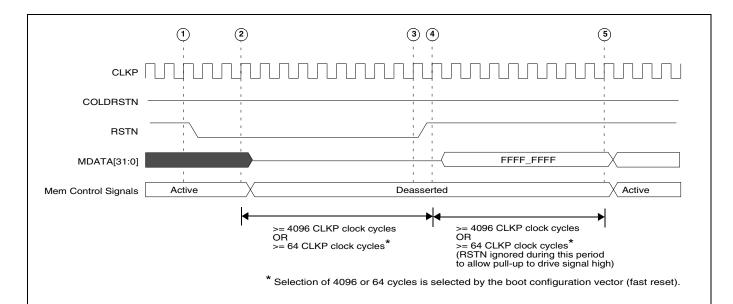

The boot configuration vector is read into the RC32351 during cold reset. The vector defines parameters in the RC32351 that are essential to operation when cold reset is complete.

The encoding of boot configuration vector is described in Table 2, and the vector input is illustrated in Figure 6.

<sup>&</sup>lt;sup>1.</sup> Schmitt Trigger Input.

| MDATA[2:0]  Clock Multiplier. This field specifies to 0x0 - multiply by 2 0x1 - multiply by 3 0x2 - multiply by 4 0x3 - reserved 0x4 - reserved 0x5 - reserved 0x6 - reserved 0x7 - reserved 0x7 - reserved | he value by which the system clock (CLKP) is multiplied internally to generate the CPU pipeline clock.                                                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MDATA[3] Endian. This bit specifies the endiann 0x0 - little endian 0x1 - big endian                                                                                                                        | ess of RC32351.                                                                                                                                                            |

| MDATA[4] Reserved. Must be set to 0.                                                                                                                                                                        |                                                                                                                                                                            |

| MDATA[5] <b>Debug Boot Mode</b> . When this bit is s 0x0 - regular mode (processor begins 0x1 - debug boot mode (processor be                                                                               |                                                                                                                                                                            |

| MDATA[7:6]  Boot Device Width. This field specific 0x0 - 8-bit boot device width 0x1 - 16-bit boot device width 0x2 - 32-bit boot device width 0x3 - reserved                                               | es the width of the boot device.                                                                                                                                           |

| MDATA[8] EJTAG/ICE Interface Enable. When selected.  0x0 - GPIOP[31, 13:10] pins behaves 0x1 - GPIOP[31] pin behaves as EJTAGPIOP[12:10] pins behave as EGPIOP[13] pin behaves as EJTA                      | AG_TRST_N,<br>JTAG_PCST[2:0], and                                                                                                                                          |

|                                                                                                                                                                                                             | 2351 drives RSTN for 64 clock cycles, used during test only. Clear this bit for normal operation. ISTN for minimum of 4096 clock cycles TN for 64 clock cycles (test only) |

| MDATA[10] DMA Debug Enable. When this bit is and peripheral bus DMA transactions. 0x0 - GPIOP[8, 9, 25, 23] pins behave 0x1 - GPIOP[8, 9, 25, 23] pins behave                                               |                                                                                                                                                                            |

|                                                                                                                                                                                                             | ns that do not require a SYSCLKP output and can instead use CLKP, setting this bit to a one causes the tant level. This may be used to reduce EMI.                         |

| MDATA[12] JTAG Boundary Scan Reset Enable 0x0 - GPIOP[2] pin behaves as GPIOI 0x1 - GPIOP[2] pin behaves as JTAG                                                                                            |                                                                                                                                                                            |

| MDATA[13] CPU / DMA Transaction Indicator E 0x0 - GPIOP[4] pin behaves as GPIOI 0x1 - GPIOP[4] pin behaves as CPUP                                                                                          |                                                                                                                                                                            |

| MDATA[15:14] Reserved. These pins must be driven                                                                                                                                                            | low during boot configuration.                                                                                                                                             |

Table 2 Boot Configuration Vector Encoding

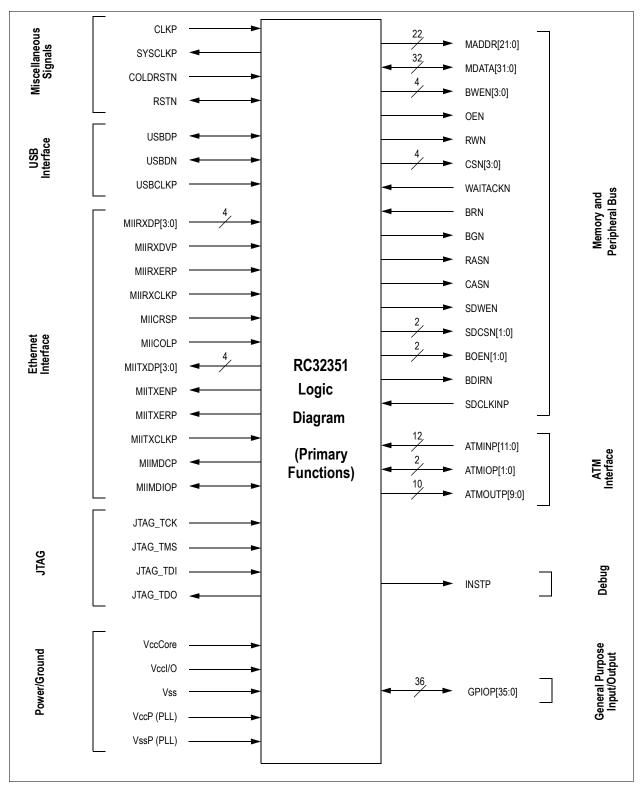

### **Logic Diagram**

The following Logic Diagram shows the primary pin functions of the RC32351.

Figure 3 Logic Diagram

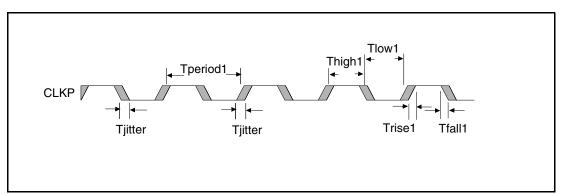

### **Clock Parameters**

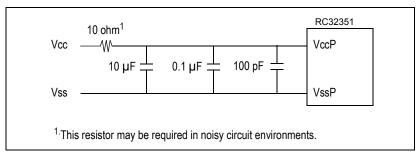

(Ta = 0°C to +70°C Commercial, Vcc I/O = +3.3V $\pm$ 5%, V<sub>cc</sub> Core and V<sub>cc</sub>P = +2.5V $\pm$ 5%)

| Parameter                                | Symbol    | Reference | RC32351<br>100MHz |      | RC32351<br>133MHz |      | Units | Timing<br>Diagram |

|------------------------------------------|-----------|-----------|-------------------|------|-------------------|------|-------|-------------------|

|                                          |           | Edge      | Min               | Max  | Min               | Max  |       | Reference         |

| Internal CPU pipeline clock <sup>1</sup> | Frequency | none      | 100               | 100  | 100               | 133  | MHz   | Figure 4          |

| CLKP <sup>2,3,4</sup>                    | Frequency | none      | 25                | 50   | 25                | 67   | MHz   |                   |

|                                          | Tperiod1  | =         | 20                | 40   | 15                | 40   | ns    |                   |

|                                          | Thigh1    | =         | 10                | _    | 6                 | _    | ns    |                   |

|                                          | Tlow1     | =         | 10                | _    | 6                 | _    | ns    |                   |

|                                          | Trise1    | =         | _                 | 3    | _                 | 3    | ns    |                   |

|                                          | Tfall1    |           | _                 | 3    | _                 | 3    | ns    |                   |

|                                          | Tjitter   |           | _                 | ±250 | _                 | ±250 | ps    |                   |

**Table 3 Clock Parameters**

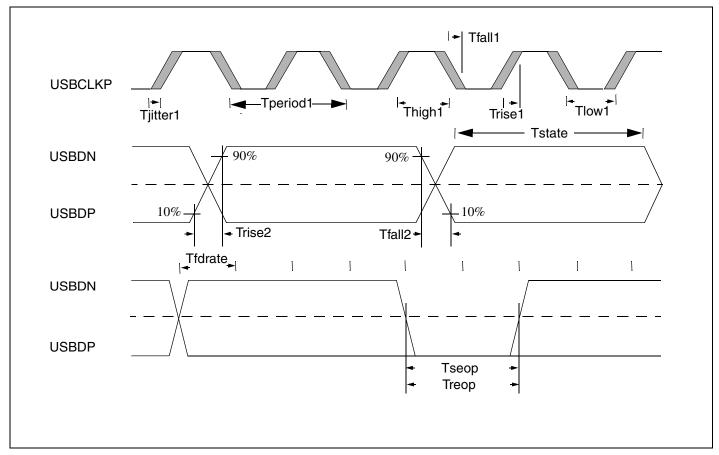

Figure 4 Clock Parameters Waveform

<sup>&</sup>lt;sup>1</sup> The CPU pipeline clock speed is selected during cold reset by the boot configuration vector (see Table 2).

<sup>2</sup> Ethernet clock (MIIRXCLKP and MIITXCLKP) frequency must be equal to or less than 1/2 CLKP frequency.

USB clock (USBCLKP) frequency must be less than CLKP frequency.

ATM Utopia clock (RXCLKP and TXCLKP) frequency must be equal to or less than 1/2 CLKP frequency.

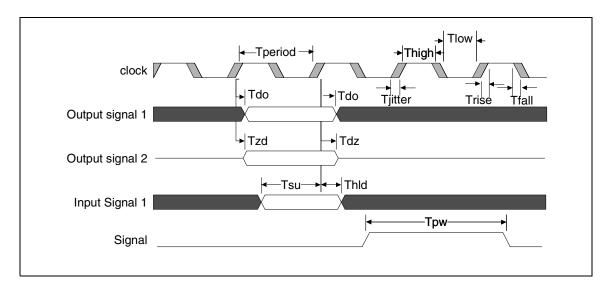

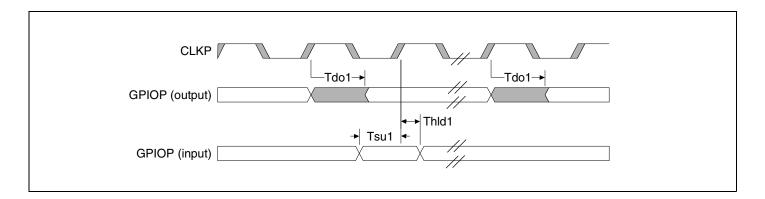

### **AC Timing Definitions**

Below are examples of the AC timing characteristics used throughout this document.

Figure 5 AC Timing Definitions Waveform

| Symbol  | Definition                                                                                                                                                                                                                |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Tperiod | Clock period.                                                                                                                                                                                                             |

| Tlow    | Clock low. Amount of time the clock is low in one clock period.                                                                                                                                                           |